内存技术的"纳米级跃进" 2025年,美光科技率先量产的1γ(1-gamma)制程节点DDR5 DRAM,标志着内存行业正式进入10nm以下工艺时代。这款被业界称为"算力催化剂"的产品,不仅刷新了性能、密度与能效的三重标准,更成为AI算力爆发式增长的关键基础设施。

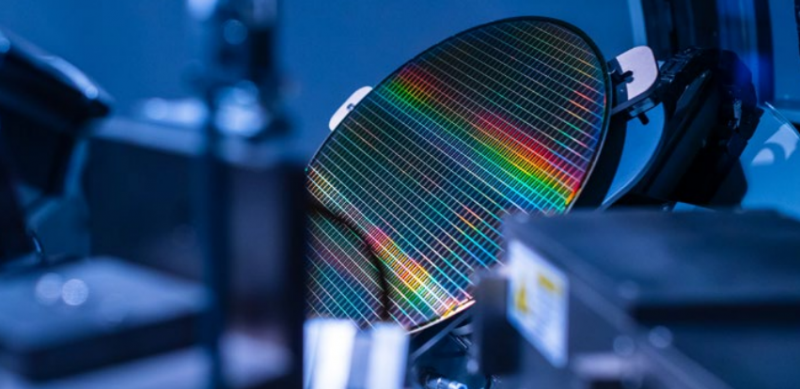

1γ工艺:技术解剖与突破性创新 1. 制程革命的物理密码 极紫外光刻(EUV)应用:首次在DRAM量产中引入5层EUV光刻,晶体管密度较1α节点提升40%,单位面积存储容量突破24Gb。 高深宽比电容结构:采用新型柱状电容设计,电荷存储能力提升35%的同时,漏电流降低至前代的1/8。 自对准四重成像(SAQP):通过多重曝光技术实现15nm级栅极间距,晶圆良品率稳定在92%以上(行业平均约85%)。 2. 性能参数颠覆式提升 速率跃迁:基础频率达7200MHz,超频模式下突破8800MHz,较上代DDR5提速22%。 能效比优化:工作电压降至1.0V,同负载下功耗节省18%,TPP(总功耗性能比)指标领先竞品1.8倍。 延迟控制:CAS延迟(CL)压缩至28,突发传输长度扩展至BL32,特别适配AI推理中的不规则数据流。

场景革命:1γ DDR5的落地实践 1. AI算力集群的"血液系统" 大模型训练加速:在256卡GPU集群中,1γ DDR5使参数交换带宽提升至3.2TB/s,ResNet-50训练时间缩短至43分钟(传统方案需68分钟)。 内存计算(PIM)支持:通过近存计算架构,矩阵乘法指令延迟降低60%,Llama 3推理吞吐量实现2.3倍增长。 2. 云数据中心的"绿色引擎" TCO优化案例:某超大规模云服务商部署后,单机架内存容量达12TB,数据中心PUE值下降至1.15,年节电超280万度。 冷数据分层存储:结合CXL 2.0协议实现动态内存池化,闲置内存利用率从35%提升至89%。 3. 边缘计算的"微型大脑" 车载域控制器实测:在L4级自动驾驶系统中,1γ DDR5的-40℃~125℃宽温特性,使内存错误率降低至1E-18 FIT(故障间隔时间)。 工业物联网响应:512GB内存模组支持2000+传感器毫秒级数据处理,西门子工厂实测延迟波动小于3μs。 产业影响与未来展望 1. 供应链格局重塑 美光西安工厂1γ产线投产,月产能达40万片晶圆,推动中国区DRAM自给率提升至28%。 长鑫存储等国内厂商加速19nm工艺研发,行业进入技术追赶"窗口期"。 2. 标准演进路线图 DDR5-8800规范冻结:JEDEC已基于1γ特性制定新标准,预计2026年完成认证。 CXL 3.0内存池化:美光实验室数据显示,1γ DDR5在内存分解架构下可实现92%的资源利用率。 3. 量子计算协同潜力 与硅基量子比特控制器的联调测试中,1γ DDR5展现出皮秒级响应能力,为混合计算架构铺平道路。

内存墙破壁者的时代使命 当ChatGPT-5需要PB级参数实时调优,当数字孪生城市要求纳秒级数据同步,1γ DDR5代表的已不仅是硬件迭代,更是算力民主化的基础设施。在这场没有终点的技术马拉松中,美光正用纳米级的精确度,重新定义计算的边界。 |

- 美光半导体NAND技术引领智能设备存储革命(2025-05-22)

- 睿创微纳AI芯片技术登上体系结构顶会,推动红外成像质量全面提升(2025-05-19)

- 欧恩贝《解密成分的力量》全网上线:揭晓刘少伟领衔HMO科研纪实历程(2025-05-06)

- 用新范式破解旧世界解释权,解密吉斯波尔的多重颠覆(2025-03-18)

- 裕太微车载芯片在汽车领域应用持续深化(2025-03-03)

- 工信部明确万兆光网试点计划,裕太微2.5G PHY芯片助力产业升级(2025-03-03)